# **CAPITULO IV-Multietapas de Bajo Nivel Amplificador Diferencial y Fuentes de Corriente**

#### IV.1. - INTRODUCCION:

Como Multietapas denominamos a todos aquellos dispositivos amplificadores que se encuentran constituidos por más de un elemento activo amplificador o etapa amplificadora, vale decir que en dichos amplificadores debe encontrarse necesariamente un **acoplamiento** entre transistores (tanto bipolares como unipolares o una combinación de estos).

A este nuevo tipo de dispositivos amplificadores se los suele clasificar de acuerdo al tipo de circuito de acoplamiento que utilicen en: Amplificadores de Corriente Continua por un lado, en Amplificadores que no amplifican la frecuencia cero y en aquellos que emplean el Optoacoplamiento. Dejando de lado a los que emplean optoacopladores, en el primer grupo recién definido se utilizan circuitos de acoplamiento directo (que acoplan C.C. y señal simultáneamente), mientras que en los restantes, principalmente en bajo nivel y bajas frecuencias se utiliza el llamado acoplamiento a resistencia-capacidad (o acoplamiento a RC).

El acoplamiento capacitivo entre etapas, que en lo precedente se ha utilizado y justificado ampliamente para conectar Cargas o Excitadores a la etapa amplificadora, si bien presenta la ventaja de permitir independizar las condiciones operativas de C.C. respecto al resto del circuito acoplado, presenta el inconveniente de una disminución de la ganancia a medida que bajan las frecuencias de operación debido a la limitación práctica de lograr capacitores tan altos como para permitir el paso de la frecuencia cero.

En un gran número de aplicaciones no reviste importancia la información que puede hallarse contenida entre la frecuencia cero y el límite inferior de frecuencias a partir del cual el acoplamiento a RC puede ser efectivo, en tanto que el hecho de mantener independizadas a las componentes estáticas de cada parte o etapa acoplada hace sumamente ventajosa la utilización de este tipo de configuraciones amplificadoras denominadas en general como Multietapas con Acoplamiento de Alterna.

Desde el punto de vista de su estudio este tipo de dispositivos de acoplamiento de alterna resultan sumamente sencillos de analizar ya que solo bastará remarcar, respecto a lo visto en monoetapas, la importancia de haber definido a las Resistencias de Entrada y de Salida de la etapa amplificadora ( $R_{iA}$  y  $R_{oA}$ ) que al analizar una etapa contigua se deberán interpretar como resistencia equivalente de carga o de excitación ( $R_{iA}$  de la etapa siguiente se debe interpretar como  $R_L$  de la anterior y  $R_{oA}$  de la etapa precedente debe estudiarse como la  $R_s$  de la etapa posterior). El Método de estudio es entonces analizar etapa por etapa tanto las condiciones de operación estáticas como dinámicas, lo cual significa respecto a lo ya visto solo un mayor volumen de trabajo.

En cuanto a los amplificadores de continua puede anticiparse una muy importante desventaja respecto de los anteriores en cuanto a que cualquier desplazamiento de las componentes de reposo de una etapa previa (debido a una variación térmica por ejemplo) es amplificado por las etapas posteriores a causa del mismo tipo de acoplamiento y puede llegarse a producir una operación en el corte o en la saturación en las etapas finales de la cadena. También es muy importante la ventaja ya que un buen número de aplicaciones requiere que el amplificador procese linealmente a las componentes de C.C.

De hecho todos los circuitos amplificadores integrados lineales son de acoplamiento directo, debido además, a la dificultad tecnológica de integrar valores apreciables de capacidad en volúmenes de integración adecuados.

En este trabajo estudiaremos a ambos tipos de circuitos amplificadores multietapa, dedicándose con mayor énfasis al estudio de aquellos con acoplamiento directo, ya que constituyen la base de la electrónica analógica integrada de actualidad. Además por su simplicidad, la otra variante de acoplamiento será considerada a través de algunos ejemplos típicos.

Consecuentes con ello y entrando ya a la categoría de amplificadores multietapa de acoplamiento directo pueden detectarse ciertas conexiones o arreglos muy frecuentemente utilizados y que proporcionan desempeños bien definidos y particulares y es sobre la base de su comportamiento en que se hallan basados los circuitos lineales integrados; ellos son a veces denominados subcircuitos y un ejemplo claro lo constituyen el Amplificador Diferencial y las Fuentes de Corriente Activas, que por lo tanto pasaremos a estudiar seguidamente.

## IV.2.- AMPLIFICADORES DIFERENCIALES:

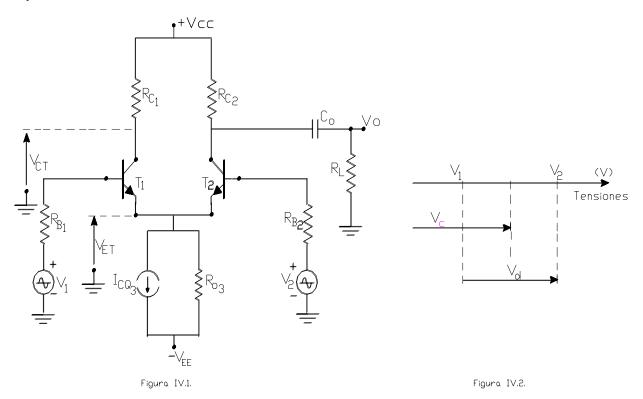

Analizaremos la configuración circuital más sencilla, aunque no práctica, correspondiente a un amplificador diferencial bipolar, tal como se muestra en la figura IV.1.

El circuito presentado, un tanto elemental y teórico, no incluye al circuito de polarización comúnmente llamado Fuente de Corriente ya que estas serán motivo de un estudio particular y por ahora la representamos mediante un circuito equivalente de Norton: es decir un generador de corriente  $I_{CQ3}$  en paralelo con su respectiva resistencia interna  $R_{o3}$ , circuito que sin mayor análisis puede asociarse con la salida de un tercer transistor.

Asimismo, para este estudio asumiremos que existe una exacta simetría entre las dos ramas del amplificador diferencial, sobre todo en lo que respecta a los transistores y a las resistencias del circuito de base de los mismos. Si bien en esta oportunidad supondremos también que ambas resistencias de colector son igualmente coincidentes, veremos más adelante que este aspecto de la simetría no es en realidad muy necesario y de hecho muchos circuitos prácticos no lo respetan.

#### IV.3.1.- Estudio del Comportamiento Estático:

Al iniciar el estudio comenzaremos por determinar las condiciones estáticas de funcionamiento de los transistores  $T_1$  y  $T_2$ . En tal sentido, dadas las condiciones de simetría impuestas para las mallas de entrada de ambos transistores y la identidad en las características base-emisor de los mismos, la corriente  $I_{CQ3}$  se dividirá en dos partes exactamente iguales, una para cada una de las ramas diferenciales. Dicho lo cual puede aceptarse que:

$$I_{CQ1} = I_{CQ2} = \frac{I_{CQ3}}{2}$$

(IV.1.)

Si bien lo que sigue resulta dependiente de los valores que adopten los componentes  $R_{B1}=R_{B2}$ , ocurre regularmente que las pequeñas caídas que producen las corrientes de base de ambos transistores resultan despreciables, sobre todo si las ganancias estáticas de corriente de los mismos es apreciable, tal es así que en la totalidad de los casos pueden despreciarse frente a la tensión base-emisor de umbral de los transistores  $(V_{BEu})$ , de modo que con muy pequeña cuota de error puede afirmarse que planteando las ecuaciones de ambas mallas equivalentes estáticas  $(v_1=v_2=0)$  de entrada:

$$V_{ET1} = V_{ET2} = -V_{BEu1-2} = -0.6 \text{ } \acute{o} -0.7 \text{ V}$$

(IV.2.)

Por otra parte, si planteáramos las ecuaciones de las mallas equivalentes estáticas de salida de ambos transistores se tiene:

$$V_{CT1-2} = V_{CC} - I_{CO1-2} . R_{C1-2}$$

y dado que:

$$V_{CEQ1-2} = V_{CT1-2C} - V_{ET1-2}$$

teniendo en cuenta la (IV.2.):

$$V_{CEO1-2} = V_{CC} + 0.6 (V) - I_{CO1-2} \cdot R_{C1-2}$$

(IV.3.)

quedando claro que tanto los valores absolutos como las condiciones de estabilización de dichas componentes de reposo resultan dependientes de las características del circuito de la Fuente de Corriente que proporciona  $I_{CO3}$ .

Puede observarse asimismo que si las resistencias del circuito de colector de ambas ramas diferenciales no fueran idénticas como se ha planteado, lo único que ocurriría es que los transistores, trabajando ambos a la misma corriente de polarización, se hallarían sometidos a diferentes tensiones colector-emisor de reposo ( $V_{CEQ1}$  diferente a  $V_{CEQ2}$ ), lo cual, dentro de límites aceptables, no introduciría diferencias apreciables en el comportamiento dinámico de ambos transistores, ya que como se vio dichos parámetros dinámicos no son fuertemente dependientes de dicha tensión de reposo  $V_{CEQ}$ , por lo menos no como lo son respecto de la corriente  $I_{CO}$ .

#### IV.3.2.- Análisis del Comportamiento Dinámico:

Con la finalidad de encarar el estudio del funcionamiento del circuito frente a señales de bajo nivel, en este caso previamente haremos algunas definiciones que resultan imprescindibles, entre otras razones, para permitir una simplificación de la tarea, a la par de hacer uso de ciertos parámetros un tanto particulares que los propios fabricantes de circuitos integrados utilizan para describir y valorizar el funcionamiento de sus productos.

Llamaremos entonces TENSIÓN DE MODO DIFERENCIAL DE ENTRADA o simplemente Modo Diferencial de Excitación o modo diferencial, a la diferencia entre las dos tensiones de excitación dispuestas en el circuito. Ello con independencia de que ambas existan simultáneamente en una aplicación real o bien con independencia de su valor. En consecuencia dadas las  $v_1$  y  $v_2$  por definición la tensión de excitación de modo diferencial  $v_d$  es:

$$v_d = v_1 - v_2$$

(IV.4.)  $v_c = \frac{v_1 + v_2}{2}$  (IV.5.)

La expresión (IV.5.) representa otra definición, la correspondiente a la TENSIÓN DE MODO COMÚN DE ENTRADA que como se ve puede interpretarse como el promedio entre las dos tensiones de entrada. Cabe aclarar al respecto que puede encontrarse bibliografía en donde tales definiciones difieran respecto a lo precedentemente expresado y que en este trabajo se optado por ellas para ajustarla a las especificaciones más comunes de los Manuales de los fabricantes de componentes.

En la figura IV.2. se lleva a cabo una interpretación gráfica de una situación dada y arbitraria en un instante de tiempo determinado para ambas tensiones de excitación  $v_1$  y  $v_2$  y los modos recién definidos.

. Como corolario de tal observación las tensiones de excitación originales de ambas bases pueden ser descriptas en función de ambos modos ya definidos:

$$v_2 = v_c + \frac{v_d}{2}$$

$y v_1 = v_c - \frac{v_d}{2}$  (IV.6.)

Volviendo a nuestro circuito amplificador diferencial digamos que en él se busca por sobre cualquier otra característica, que:

$$v_0 = K \cdot v_d$$

Desafortunadamente ello es solo posible en un amplificador diferencial ideal, ya que en la práctica, en la salida de dicho circuito se tendrá en general una tensión de salida formada por una parte proporcional a la tensión diferencial  $v_d$  y otra parte proporcional a la tensión de modo común  $v_c$ , vale decir:

$$v_o = v_{od} + v_{oc}$$

Llamando Ganancia de Tensión de Modo Diferencial o simplemente **Amplificación Diferencial**  $(A_{vd})$  y Ganancia de Tensión de Modo Común o bien **Amplificación de Modo Común**  $(A_{vc})$ , a la relaciones:

$$A_{vd} = \frac{V_{od}}{V_{od}}$$

(IV.7.)  $y$   $A_{vc} = \frac{V_{oc}}{V_{c}}$  (IV.8.)

la tensión de salida de la etapa diferencial puede expresarse según:

$$v_{o} = A_{vd} \cdot v_{d} + A_{vc} \cdot v_{c}$$

o bien:  $v_{o} = A_{vd} \cdot v_{d} \cdot (1 + \frac{v_{c} / v_{d}}{-----})$

Esta última expresión detalla lo dicho respecto a la conformación de la tensión de salida de la etapa y puede observarse que tal como se adelantara, los resultados obtenidos a la salida del circuito amplificador difieren notoriamente respecto de lo esperado, ya que además de la parte de  $v_o$  dependiente de la señal diferencial de excitación  $v_d$  ( $A_{vd}$  .  $v_d$ ), se incluye un error (relativo)  $\epsilon$  expresado por:

$$\varepsilon = \frac{v_c / v_d}{A_{vd} / A_{vc}}$$

y que para minimizarlo, cualquiera sea el tipo de excitación presente  $(v_c / v_d)$  debe conseguirse que:

$$A_{vd} >> A_{vc}$$

Para poder cuantificar esta característica del circuito, se define el parámetro llamado RELACION DE RECHAZO DE MODO COMUN (C.M.R.R. =  $\rho$  ):

C.M.R.R. =

$$\rho = \frac{A_{vd}}{A_{vd}}$$

(IV. 9)

con lo cual la expresión de la tensión de salida de la etapa diferencial resulta:

$$v_{o} = A_{vd} \cdot v_{d} \cdot (1 + \frac{v_{c} / v_{d}}{\rho})$$

(IV.10.)

En dicha relación, el término dependiente de la C.M.R.R. expresa la característica real del circuito y su valorización en la práctica permitirá determinar la medida en que el amplificador diferencial real (C.M.R.R. finito) se aparta del circuito ideal para el cual C.M.R.R. resulta infinito.

La realidad práctica si bien no permite en la actualidad obtener comportamientos diferenciales ideales, consigue circuitos amplificadores diferenciales que presentan C.M.R.R. suficientemente elevadas como para poder tolerar perfectamente los pequeños errores que subsisten.

Es así que a la fecha resultan incontables las aplicaciones que se pueden encontrar en la utilización de los circuitos amplificadores diferenciales, cuya característica dinámica de funcionamiento quedó representada por la ecuación (IV.10.) precedente. Desde su desempeño como dispositivo de mezcla o comparación entre una señal de referencia y otra exterior en cualquier sistema de control, pasando por el empleo como etapa separadora de una señal útil entre otras interferentes, hasta llegar a convertirse en la etapa de entrada de cualquier Amplificador Operacional, como veremos más adelante en este trabajo.

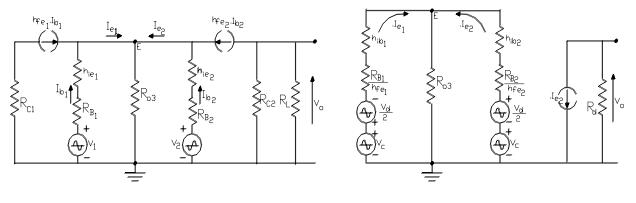

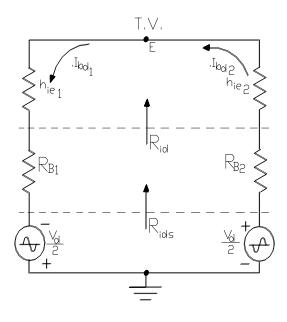

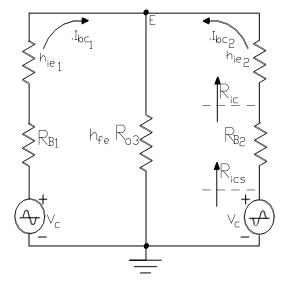

Por ahora nos interesa encontrar cuales son las relaciones que vinculan a los parámetros dinámicos recién definidos y las constantes de los componentes del circuito bajo estudio. Con ese objetivo y al imponer las condiciones de funcionamiento de bajo nivel y bajas frecuencias, representamos a dicho circuito haciendo uso del modelo híbrido simplificado para reemplazar a ambos transistores, resultando un circuito equivalente tal como el representado en la figura IV.3.

Figura IV.3. Figura IV.4.

A partir de este circuito, desdoblando las fuentes controladas  $I_{c2}$  ( $h_{fe}$  .  $I_{b2}$ ) e  $I_{c1}$  ( $h_{fe}$  .  $I_{b1}$ ) según procedimiento ya estudiado con anterioridad, despreciando la parte de salida de  $T_1$  (ya que su colector no se carga para la señal), y absorbiendo los generadores (tanto para  $T_1$  como para  $T_2$ ) del circuito de entrada por modificación de las corrientes de malla y cambio de las impedancias correspondientes, es posible pasar a estudiar el circuito equivalente representado en la figura IV.4. En este último además se reemplazaron los generadores de excitación de acuerdo a las definiciones de los dos modos de excitación, se tuvo en cuenta que la resistencia de carga dinámica es  $R_d = R_L \ /\!/ R_{C2} \ /\!/ r_o$  y que la expresión (II.45.) establece una relación entre los parámetros  $h_{ib}$  y  $h_{ie}$ .

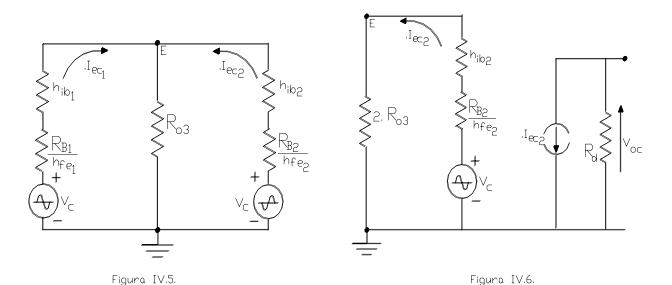

Obtenemos así un circuito en donde intervienen dos fuentes de excitación dinámicas ( $v_c$  y  $v_d/2$ ) por lo que para estudiar su comportamiento total, dada la condición de linealidad impuesta, es posible aplicar el principio de superposición. En tal sentido, en primer lugar analizamos su comportamiento frente a la acción de la señal de modo común ( $v_c$ ), anulando simultáneamente a la señal de modo diferencial ( $v_d$ ) con lo que la parte de entrada del circuito resultante se reduce al esquema representado en la figura IV.5.

En dicho circuito las corrientes de ambas mallas, es decir las que hemos llamado  $I_{ec1}$  e  $I_{ec2}$  (corrientes de emisor para el modo común de excitación) serán idénticas en magnitud y fase atento las condiciones de simetría de ambas mallas, de modo que por la resistencia  $R_{o3}$  se tendrá una corriente total que puede ser:

$$2 . I_{ec1} = 2 . I_{ec2}$$

Entonces nuevamente se podrá pasar a otro circuito equivalente, valido únicamente para la señal de modo común, que solo represente la parte correspondiente al transistor al cual se halla conectada la carga (T<sub>2</sub>) pero sin dejar de considerar la presencia y actividad del transistor restante. Esto se ha logrado en el circuito equivalente indicado en la figura IV.6. en donde para tener en cuenta lo dicho en el último párrafo se ha duplicado la resistencia de la rama central del

circuito de la figura IV.5. (2 .  $R_{o3}$ ) que permite mantener la caída de tensión en dicha rama cuando actúa un solo transistor. Debe observarse asimismo que en el último circuito se ha agregado la parte de salida del transistor  $T_2$ , dado que seguidamente procedemos a determinar la tensión de salida para el modo común ( $v_{oc}$ ).

$$v_{oc} = \text{-} \ I_{ec2} \ . \ R_d \qquad \qquad con \qquad \qquad I_{ec2} = \frac{v_c}{2 \ . \ R_{o3} \ + \ h_{ib1-2} \ + (R_{B1-2} \ / \ h_{fe1-2})}$$

esta última expresión, dado los valores usuales que adoptan tanto R<sub>o3</sub> como los restantes dos términos del denominador, puede aproximarse con error despreciable y entonces describir a la tensión de salida como:

$$v_{oc} = - \frac{v_c \cdot R_d}{1 \cdot 1 \cdot 1}$$

(IV.11.) y la ganancia de tensión de modo común:  $A_{vc} = - \frac{R_d}{1 \cdot 1 \cdot 1}$  (IV.11.)  $2 \cdot R_{o3}$

es decir que la ganancia de tensión de modo común, además de ser proporcional a la carga dinámica del transistor, resulta inversamente proporcional a la resistencia de salida de la fuente de corriente de polarización.

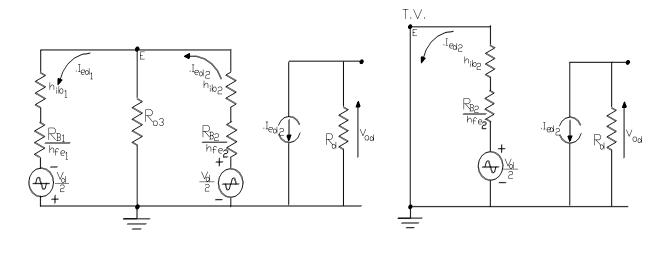

Volvamos ahora al circuito equivalente completo y pongamos en práctica el segundo paso del principio de superposición, anulando ahora a la señal de modo común y estudiando el comportamiento del circuito frente a la señal de excitación de modo diferencial. El circuito equivalente que representa esta condición se indica en la figura IV,7,

En este circuito, dada la oposición de fase entre los generadores de tensión de excitación de modo diferencial, en la entrada, por la rama central que contiene a  $R_{o3}$  no se registra ninguna corriente por lo que en ella no se desarrolla diferencia de potencial alguna debido a este modo, en razón de que el balance de ambas ramas es perfecto. Si en  $R_{o3}$  no se desarrolla diferencia de potencial diferencial, se puede realizar otro circuito equivalente al precedente pero de uno solo de los transistores, nuevamente el  $T_2$  que es el que se halla cargado, pero otra vez sin dejar de considerar la presencia del transistor restante. Ello se concreta en el circuito equivalente de la figura IV.8.

Puede constatarse que en la figura IV.8. se ha tenido en cuenta la presencia del transistor T a través de la consideración de que el nodo unión de emisores (E) se comporta como una "Tierra Virtual", derivado de que al no existir caída en R<sub>o3</sub> dicho nodo se encuentra virtualmente conectado a masa para dicha señal diferencial. El estudio de las mallas de entrada y de salida de dicho circuito equivalente dinámico nos permite escribir las siguientes ecuaciones:

$$v_{od} = -\ I_{ed2}\ .\ R_d \qquad \qquad con \qquad \qquad I_{ed2} = \frac{v_d}{2\ .\ [\ h_{ib1-2}\ + (R_{B1-2}\ /\ h_{fe1-2})]}$$

Figura IV.8

luego reemplazando I<sub>ed2</sub> en v<sub>od</sub> se obtiene:

Figura IV.7.

IV - Multietapas de Bajo Nivel: Amplificador Diferencial y Fuentes de Corriente

que también puede escribirse como:

$$A_{vd} = \frac{-h_{fel-2} \cdot R_d}{2 \cdot (h_{iel-2} + R_{Bl-2})}$$

(IV.14'.)

arrojando como resultado una ganancia igual a la mitad de la que le correspondería a una etapa emisor común con igual carga.

Continuando con la aplicación del principio de superposición, llevamos a cabo ahora el tercer paso, es decir que hallamos el total de la tensión de señal a la salida sumando los productos de dicha componente para cada uno de los modos de entrada que nos proporcionan las expresiones (IV.11.) y (IV.13.), vale decir:

$$v_{o} = v_{oc} + v_{od}$$

$$v_{o} = v_{c} \cdot \frac{-R_{d}}{2 \cdot R_{o3}} + v_{d} \cdot \frac{-h_{fel-2} \cdot R_{d}}{2 \cdot (h_{iel-2} + R_{Bl-2})}$$

(IV.15.)

que resulta concordante con lo expresado por la ecuación (IV.10.) de modo que reemplazando en la definición de la Relación de Rechazo de Modo Común se obtiene:

C.M.R.R. =

$$\rho = \frac{R_{o3}}{h_{ib1-2} + (R_{B1-2}/h_{fe1-2})}$$

(IV.16.)

Algunas conclusiones pueden mencionarse al analizar los resultados obtenidos hasta aquí:

a) el apartamiento o error existente entre el comportamiento del amplificador diferencial real y el ideal ( $\epsilon$ ) no solo depende

de la relación de rechazo de modo común  $(C.M.R.R. = \rho)$  sino que igualmente es función de la relación entre los valores que asuman los modos diferencial y común de excitación  $(v_c / v_d)$ . Algunos ejemplos numéricos desarrollados más adelante nos ilustran al respecto.

b) es posible reducir dicho apartamiento, independientemente de la relación de los modos de excitación, haciendo al rechazo todo lo grande como sea posible (idealmente infinito), para lo cual resulta necesario polarizar a la configuración diferencial con fuentes de corriente de gran resistencia de salida (idealmente R<sub>o3</sub> infinito).

Observemos algunos resultados numéricos. Supongamos en tal sentido los siguientes casos:

1°)  $v_1 = 50 \text{ mV}$ ;  $v_2 = -50 \text{ mV}$ . Para: a)  $\rho = 10$ ; b)  $\rho = 100$ ; c)  $\rho = 1000$ . Se pide determinar el error debido a la eventual presencia de modo común de excitación.

Dado que  $v_d =$  -100 mV y  $v_c = 0$ , independientemente de los valores de  $\rho$  el error es nulo, es decir:

$$\varepsilon_{a} = \varepsilon_{b} = \varepsilon_{c} = 0$$

a la salida del amplificador diferencial solamente se obtendrá señal proporcional a la tensión de entrada de modo diferencial.

$2^{\circ}$ )  $v_1 = 150 \text{ mV}$ ;  $v_2 = 50 \text{ mV}$ . Para iguales valores de  $\rho$  de acuerdo a lo indicado en el punto anterior, se solicita también ahora determinar el error debido a la presencia de modo común de excitación.

Nuevamente  $v_d$  = -100 mV. mientras que ahora  $v_c$  = 100 mV por lo que los errores serán, para cada relación de rechazo:

$$\varepsilon_{a} = 10 \% - \varepsilon_{b} = 1 \% - \varepsilon_{c} = 0.1 \%$$

$3^{\circ}$ )  $v_1 = 1050 \text{ mV}$ ;  $v_2 = 950 \text{ mV}$ . y nuevamente para iguales valores de una vez mas se requiere determinar los errores en cada caso.

En este caso se tiene  $v_d = -100 \text{ mV}$  y ahora la tensión de modo común de excitación resulta  $v_c = 1000 \text{ mV}$ . Los errores resultantes son:

$$\varepsilon_a = 100 \% - \varepsilon_b = 10 \% - \varepsilon_c = 1 \%$$

Debiéndose notar que para disminuir estos errores por debajo del 0,1 % se deben conseguir relaciones de rechazo de 10<sup>4</sup> o más.

Estudiaremos ahora las Resistencias de Entrada y de Salida del Amplificador Diferencial. Para tal fin recordemos uno de los primeros circuitos equivalentes que hemos realizado en la figura IV.3. A partir de dicho circuito y con la finalidad de estudiar su transferencia, en los estudios realizados hasta aquí se procedió a uniformar la corriente de las mallas de entrada a nivel de corriente de emisor ( I<sub>e</sub> ).

Pretendemos ahora estudiar la resistencia de entrada del circuito amplificador y dado que los puntos de excitación los hemos definido en los terminales de base de los transistores, al intentar uniformar las corrientes en las dos mallas de entrada lo haremos tomando como referencia a la corriente de base ( $I_b$ ). Tal procedimiento lo pondremos en práctica para cada uno de los dos tipos de señales de excitación.

En primer lugar, para la señal diferencial, atento a la característica de TIERRA VIRTUAL del terminal de unión de los emisores ( Nodo E ), la malla de entrada uniformada, solo para la corriente de base diferencial se representa en la figura IV.9.

A partir de allí, la resistencia de entrada Diferencial del amplificador resultará:

$$R_{id} = 2 . h_{ie1-2}$$

(IV.17.)

Figura IV.9.

Figura IV.10.

mientras que si consideramos a la resistencia interna de los generadores de excitación, la resistencia de entrada Diferencial del sistema amplificador será:

$$R_{ids} = 2 \cdot (h_{ie1-2} + R_{B1-2})$$

(IV.18.)

Para la señal de modo común en cambio, el circuito equivalente de las mallas de entrada, uniformado a nivel de corriente de base de modo común ( $I_{bc}$ ) se representa en la figura IV.10. y entonces las resistencias de entrada de Modo Común, tanto para el amplificador como para el sistema amplificador resultan ser:

$$R_{ic} = h_{ie1-2} + 2$$

.  $h_{fe1-2}$  .  $R_{o3}$  (IV.19.) -  $R_{ics} = R_{B1-2} + h_{ie1-2} + 2$  .  $h_{fe1-2}$  .  $R_{o3}$  (IV.20.)

#### IV.3.3.- Ejemplos de Amplificadores Diferenciales:

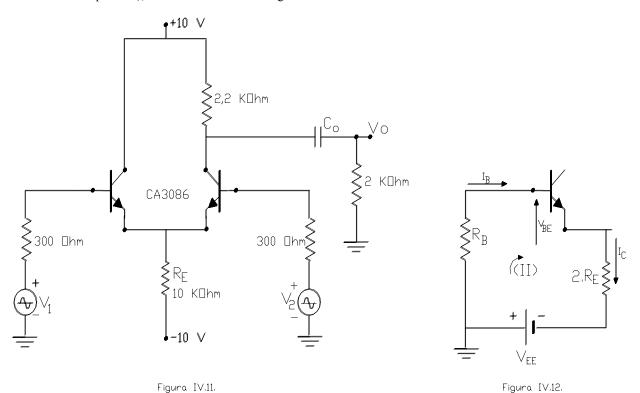

### a) Polarización con elementos pasivos

En este caso el circuito amplificador diferencial se encuentra polarizado mediante un resistor llamado R<sub>E</sub> que se conecta entre la unión de los dos emisores y la fuente de alimentación, (en este caso de polaridad negativa al tratarse de transistores del tipo NPN), tal como se indica en la figura IV.11.

Dado dicho circuito, nos proponemos verificar el comportamiento del mismo, especificando particularmente la excursión simétrica máxima potencial y la tensión de salida proporcional a la señal diferencial de entrada, así como el error debido al eventual modo común de entrada frente a las siguientes dos condiciones de excitación: 1)  $v_2 = 10 \text{ mV}$ ;  $v_1 = -10 \text{ mV y } 2$ )  $v_2 = 110 \text{ mV}$ ;  $v_1 = 90 \text{ mV}$ . Asimismo se solicita verificar cual sería la limitación que se presentaría si se pretende disminuir el error antes determinado por debajo de un 0,3 % sin modificar el esquema de circuito. Finalmente se solicitan las resistencias de entrada frente a los dos modos de excitación.

Para el análisis estático, particularmente su malla de entrada puede ser estudiada mediante el circuito equivalente presentado en la figura IV.12. Se debe constatar que el mismo solo representa la entrada de uno cualquiera de los dos transistores y para tener en cuenta la presencia del restante se ha duplicado el valor de R<sub>E</sub>. Así, en dicho circuito equivalente:

$$I_{CQ} = \frac{V_{EE} - V_{BEu}}{2 R_E + (R_B / h_{FE})}$$

$I_{CQ} = \frac{V_{EE} - V_{BEu}}{2 \ R_E + (R_B / h_{FE} \,)}$  Del Manual obtenemos que para una  $I_C = 1$  mA estos transistores integrados presentan un valor típico de  $h_{FE}$  de 100, en consecuencia dado los valores de  $R_{\rm B}\,$  y de  $\,$   $\,$   $R_{\rm E}\,$  , al reemplazarlos en la expresión anterior nos queda:

$$I_{CQ} = \frac{10 - 0.6}{2 \cdot 10^4} = 0.47 \text{ mA}$$

que es tanto válida para T<sub>1</sub> como para T<sub>2</sub>.

Asimismo, a partir del estudio de las mallas de salida de ambos transistores se tiene que:

$$V_{\text{CEQ1-2}} = V_{\text{CT1-2}} - V_{\text{ET1-2}}$$

en donde  $V_{\text{ET1-2}} = -V_{\text{BE1-2}} - I_{\text{B1-2}}$  .  $R_{\text{B1-2}} = -0.6 - (0.47/85)$  .  $300 \cdot 10^{-3} = -0.6 \text{ V}$

mientras que

$$V_{CT1} = V_{CC} = +10 \text{ V}$$

y  $V_{CT2} = V_{CC}$  -  $I_{CQ}$  .  $R_{C2} = 10$  - 0,47 .  $10^{-3}$  . 2,2 .  $10^{3} = 9 \text{ V}$  en consecuencia:  $V_{CEQ1} = 10,7 \text{ V}$  y  $V_{CEQ2} = 9,7 \text{ V}$

Verificamos en consecuencia que ambos puntos de reposo son prácticamente iguales y así los consideraremos a los efectos de obtener, a partir del Manual, los parámetros dinámicos de los transistores.

La excursión simétrica máxima posible y que para este tipo de amplificador hemos definido como "potencial", ya que como se verá más adelante la misma puede ser acotada por requerimientos de linealidad de la etapa, se obtiene analizando la separación del punto de reposo recién hallado con las zonas alineales del corte y saturación. Así

-por saturación

$$V_{odmax}$$

< (  $V_{CEQ2}$  -  $V_{CE(sat)}$  ) = 9,7 - 1 = 8,7 V

-por corte  $V_{odmax}$  < I . R = 0,47 .  $10^{-3}$  . (2,2 Kohm//2 Kohm) = 0,9 V

-la menor de las dos constituye la excursión simétrica máxima:  $V_{odmax} = 0.9 V$

En las figuras IV.13. y IV.14. se han realizado una vez más, los circuitos equivalentes respectivamente para la señal diferencial y para la señal de modo común. De dichos circuitos equivalentes se obtienen las expresiones de las ganancias de tensión, tanto de señal diferencial como de señal de modo común que utilizaremos seguidamente para las determinaciones numéricas. Previamente y a partir de las especificaciones del Manual obtenemos:

Para

$$I_C == 0.5$$

mA y  $V_{CE} = 3$  V:  $h_{ie} = 1.8 \cdot 3.5$  KOhm = 6.3 KOhm y  $h_{fe} = 1$  . 100 = 100 luego:

$$A_{vd} = \frac{-R_d}{2 \cdot [ h_{ib1-2} + (R_{B1-2} / h_{fe1-2})]} = \frac{-1900}{2 \cdot (63 + 3)} = -14.4$$

$$A_{vc} = \frac{-R_d}{2 \cdot R_E + h_{ib1-2} + (R_{B1-2} / h_{fe1-2})} = \frac{-1900}{20 \cdot 10^3 + 66} = -0,0947$$

Entonces la relación de rechazo de modo común resulta:

C.M.R.R. =

$$\rho = \frac{R_E}{h_{ib1-2} + (R_{B1-2}/h_{fe1-2})} = \frac{10^4}{63 + 3} = 151,5$$

En consecuencia , dado que para el caso 1)  $v_d$  = 20 mV y  $v_c$  = 0 ; y para el caso 2)  $v_d$  = 20 mV y  $v_c$  = 100 mV y teniendo en cuenta que:

$$v_{o}$$

=  $A_{vd}$  .  $v_{d}$  . (  $1$  +  $\stackrel{v_{c}}{-----}$  )  $\;\;$  para cada caso se tendrá: